LNAFIN Oy Participates in Alihankinta 2016 Trade Fair

Alihankinta 2016 is the foremost international industry trade fair in Finland. Industrial subcontractors have been gathering to Tampere for years to gain visibility, new business contacts and new ideas. The Alihankinta fair is held annually in Tampere Exhibition and Sports Centre, Ilmailunkatu 20, 33900 Tampere, Finland. This year’s fair has attracted 1000 exhibitors from 20 countries. As a result of that, the exhibited products and services vary tremendously. However, Alihankinta Fair main product categories have been categorized as: production methods, products and components, R&D and design services plus ICT. Thus we feel that LNAFIN Oy PCB layout design, PCB deliveries, electronics assembly, R&D services, wirebonding, prototyping and RF design know-how has something to offer for Alihankinta 2016 visitors.

Visit LNAFIN at C430 and Win!

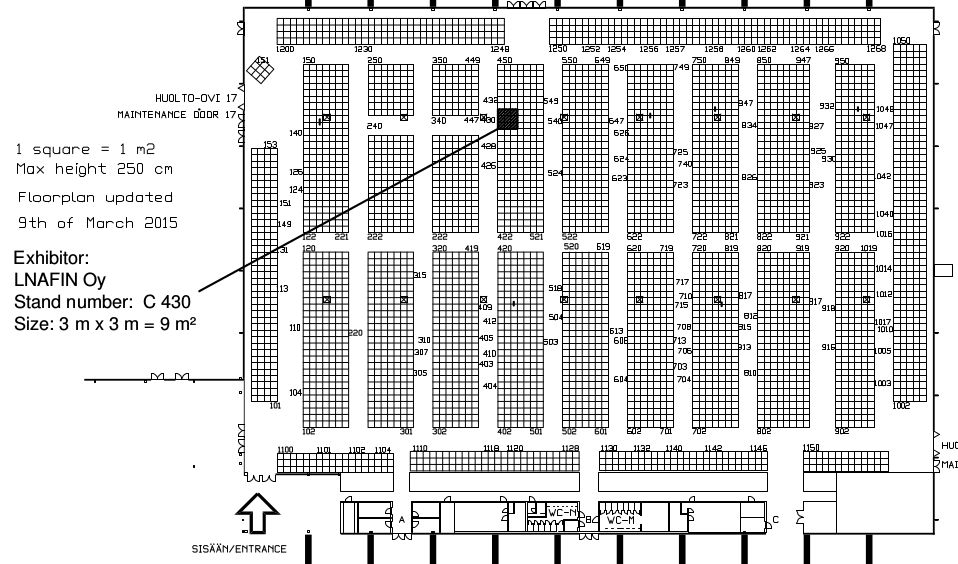

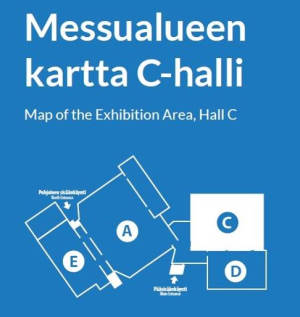

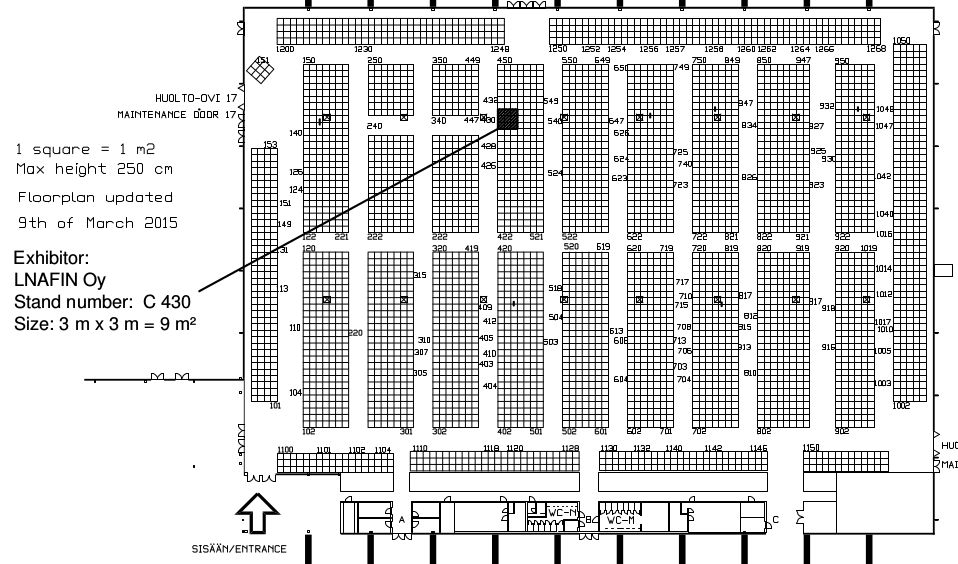

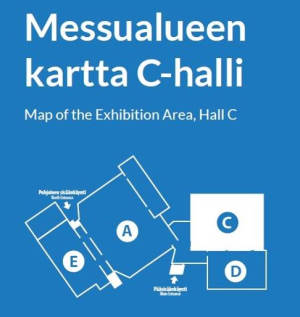

You will meet us in C-hall at our booth C430. We are very satisfied to have gotten a booth in this year’s outsold event. At the same time we wish that many fair goers would have an interest in electronics products and design services. We would be pleased to discuss circuit design and printed circuit board related prototyping/production needs. All booth visitors can take part in our small fair lottery. We will randomly draw winners to receive gift certificates for our products. Winners will be personally informed. We have included two maps of the area in this post: the blue map above shows the general exhibition area layout, whereas the black-and-white map below shows the C-hall exhibitor map.